# A LOW NOISE GM-C CHOPPER FOR ENG SIGNAL AMPLIFICATION.

Matías Miguez, Alfredo Arnaud

Depto. De Ingeniería Eléctrica - Universidad Católica del Uruguay

Contact email: meiyas@ieee.org

## **ABSTRACT**

In this paper, a chopped  $G_m$ -C filter-amplifier is presented, the circuit was designed, fabricated in a 1.5 $\mu$ m technology, and tested. The target application is ENG: nerve signal amplification, where ultra low noise and minimal power consumption are mandatory. The key aspect of chopped  $G_m$ -C technique is simplicity, allowing to achieve a reduced area, and integrating low-pass filter in the self chopper. The selected approach shows an excellent trade-off between noise, area, and power consumption, for demanding applications in the field of implantable medical electronics.

## 1. INTRODUCTION

In recent years there has been a considerable research effort in the development of integrated amplifiers for electro-neuro-graph (ENG) signal recording. ENG signals range from a few Hz to a few kHz and require an input referred noise of a few  $nV/\sqrt{Hz}$ , and a high CMRR. To reduce flicker noise, several of these circuits chopper amplifier technique A simple CMOS chopper circuit was proposed by Oswald et al. in 1984 [3] just by switching input branches of a Miller-like amplifier. But CMOS choppers have evolved since then to improve usual chopper benchmarks: reduce offset, but also noise and power consumption. A topology that became popular is to use a band-pass amplifier in between chopper modulators to reduce high-frequency spikes that introduce residual offset [4,5]. Further, in [6], nested-choppers are used to obtain an instrumentation amplifier with less than 100nV offset. But ENG amplification do not require such an extremely low input offset. In Table 1, there are compared together three works from 2004 (IEEE-ISCAS) in the field of ENG amplification. Two of them use the band-pass chopper topology to reduce flicker noise, while the third uses a non-chopped continuous time amplifier.

For a non-chopped amplifier, input referred noise is a result of power consumption and area constrains [8]:

$$v_{rms}^2 \approx \frac{A}{g_m} + \frac{B}{W.L} \tag{1}$$

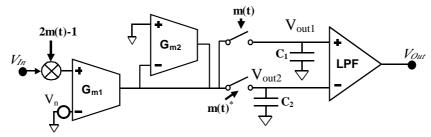

Where  $v_{nrms}$  is the input rms noise voltage in the band of interest,  $g_m, W, L$  are the input transistors transconductance, width, and length respectively. A, B, are constants depending on frequency range, and technology parameters. The first term in (1) is thermal noise contribution. the latter is associated to flicker noise. As pointed in [7,8] low input noise requires: a large bias current for a large  $g_m$  to reduce thermal noise; and a in non-chopped amplifiers a large W,L for flicker noise reduction. Chopper amplifier technique is suitable to preserve a reduced area for example in the case of multi-channel nerve signal recording [1], because it pushes flicker noise out of the band of interest. However, a complex chopper topology increases also area, and power consumption. For example, band-pass filter tuning [4] adds an extra circuit demanding a considerable silicon area. Since ENG applications do not require an extremely low residual offset, it would be better to return to a simple chopper, like the one in [3]: suitable to remove flicker noise but simple. In Fig.1, our proposed chopper amplifier is shown. The input signal  $V_{In}$  is chopped at a frequency  $f_{ch}$  - period  $T_{ch} = f_{ch}^{-1}$  - and then amplified on each phase through two independent G<sub>m</sub>-C low pass filters. The intermediate signals  $V_{out1}$ ,  $V_{out2}$  are further amplified

by means of a low-pass filter (LPF) to remove residual frequency components above the band of interest.  $V_{Out}$ is the output signal. The square wave m(t) switches the modulators.  $V_n$  represent a parasitic voltage source like for example input noise or offset. The topology is a modification of the one proposed by Bakker & Huijsing in [9], but sample & hold output is substituted by a current integration scheme embedded in the self chopper (the scheme has also been included in a general chopper analysis in [10]). The circuit is extremely simple: just two transconductors, two capacitors, and an output low pass filter. Even G<sub>m2</sub> can be substituted by an integrated resistor, and the output low-pass is not essential (it was placed just to provide a 'clean' output signal). Intermediate voltages  $V_{out1}, V_{out2}$  can be estimated assuming that are the result of applying a lowpass filter to the input voltage of the form:

Figure 1: Topology of the proposed G<sub>m</sub>-C amplifier. m(t) is a square wave signal.

$$H(\omega) = \frac{G_{m1}}{G_{m2}} \cdot \frac{1}{[1 + j\omega 2C/G_{m2}]}$$

(2)

The factor 2 of the capacitor in (2) is the result of switching the transconductances at a 50% duty cycle – see [11]-. Because the input signal  $V_{in}$  is chopped, both branches are amplifying roughly the same signal, but with opposite sign. Their output is then subtracted, the result being  $V_{Out} = H(\omega)V_{in}$ . On the other hand, noise and offset voltage at the input  $V_n$  are amplified with equal sign and then subtracted. To guarantee a proper noise cancellation, the hypothesis is that the signal  $V_n$  does not change too much from one phase to another of the chopper. This is true for offset, and flicker noise (if  $f_{ch} >> f$ ) but unfortunately not in the case of thermal

noise

$$(V_n = V_{th})$$

, where  $\int_T^{T+T_{ch}/2} V_{th}.dt$ , and  $\int_{T+T_{ch}/2}^{T+T_{ch}} V_{th}.dt$  are

non-correlated. The exact calculation of the output signal is complex because we are dealing with a non time-invariant system, where also aliasing should be considered. The detailed theory of switched filter is presented in [11].

This paper shows the implementation of a switched Gm-C filter, based on ENG amplifier specifications. In the next section amplifier design considerations are presented, while in section 3 measurement results are shown. The main advantage of this circuit is its simplicity: the low pass filter is embedded in the chopper itself. The technique is valuable for the amplification of biological signals, to remove flicker noise, and fully compatible with ultralow power circuits employed in implantable medical electronics.

# 1.1. Specifications

The circuit is intended to amplify ENG signals with amplitudes greater than  $1\mu Vp$  in the band from 100 to 5 KHz. Low noise is critical, initially specified as less than 5 nV/Hz $^{1/2}$ . Additionally, a high CMRR (~ 90dB) is expected, gain of this first stage must be at least 50, while further amplification is obtained in successive stages.

## 2. CIRCUIT DESIGN

The chopper pre-amplifier circuit was designed, fabricated in AMIS 1.5  $\mu$ m technology, and tested. The three major design constrains were obtaining low noise, while reducing area, and power consumption. To achieve low noise and current consumption it is better to polarize transistors in weak inversion, because  $g_m/I_D$  ratio is the largest, so thermal noise is the minimum at a given current (1). But unless very low currents are used, this means a high W/L ratio increasing the transistor area. In this case we set the maximum value of W/L to be 100, to prioritize the reduced area.

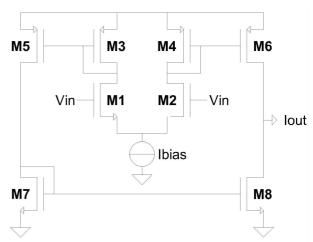

Gm1 is shown in Fig.2, it is a standard symmetrical OTA implemented using 8 transistors. The differential pair M1, M2, require the maximum W/L and were designed with W = 150  $\mu m$  and L = 1.5  $\mu m$ . The other six transistors are sized W = 150  $\mu m$  and L = 4.5  $\mu m$ . This design not only is simple, but it also uses very little area, less than 0.04  $mm^2$ , including the switching transistors for signal commutation.

A 3.4mA bias current was selected, enough large to guarantee a reduced thermal noise. A total input noise of 4 nV/ $\sqrt{\text{Hz}}$  was estimated for the circuit.

Figure 2: Implementation of Gm1.

Gm2 was substituted by an integrated poly resistance of 62 K $\Omega$ . The output capacitors were calculated to set the LPF pole at 5000 Hz. The two 300 pF double poly capacitors were integrated in the chip, increasing the total area to 1 mm<sup>2</sup>.

The circuit was simulated using BSIM3v3 model, at several operating conditions. The nominal chopper frequency is 20 KHz. The nominal gain is 70, and input signals of up to 1 mV simulated.

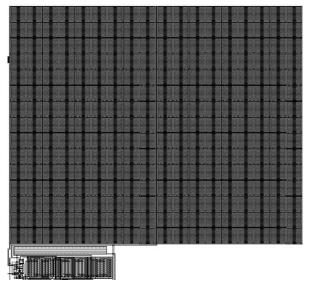

Figure 3 shows the final layout of the design.

Figure 3: Amplifier layout. Both capacitors at the top and transistors and resistance at bottom left.

## 3. MEASUREMENTS

The topology, shown in figure 4, was used to measure the amplifier. An instrumentation amplifier INA116 (www.ti.com) was used to amplify the signal. The gain of the amplifier was set to 10 during most measurements, and to 500 for noise measurements. A 5kHz LPF was implemented with an 8<sup>th</sup> order Butterworth filter using the sallen-key topology and the LT1051 (www.linear.com) operational amplifier because of its low noise. A Tektronix TDS1002 oscilloscope was used for measurements, and as a spectrum analyzer. 20 KHz chopper frequency was used for all measurements.

# Measurment Setup CLK Chopper Amplifier Amp. L.P.F.

Figure 4: Measurements Setup.

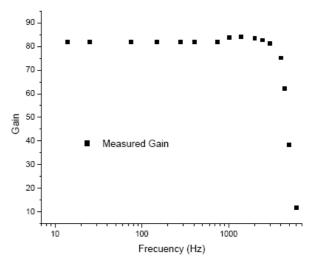

In figure 5, a graphic of Gain vs Frequency is presented. It can be seen that the gain is approximately flat in the frequency range of interest.

The measured input offset of the amplifier was approximately 2.5  $\mu V,$  in all four of the measured samples, suggesting that this is a systematic residual offset. A CMRR of 88 dB was also measured.

Measured input noise was  $1.13 \,\text{nV}/\sqrt{\text{Hz}}$  while estimated noise was  $4 \,\text{nV/Hz}^{1/2}$ . The absence of flicker noise in baseband was observed as it was expected.

The circuit properly operated up to 4V supply voltage, with a measured current consumption of 3.4mA.

Figure 5: Amplifier Gain vs Frequency.

## 3.1. Analysis of circuit results and improvements.

Although the power consumption of the amplifier is still high (28 mW), both supply voltage and polarization current can be reduced without increasing noise, by increasing W/L ratio of the transistors pushing them closer to weak inversion. As seen in figure 3, since most of the area of our circuit is taken by the integrated capacitors (more than 90 %), increasing the area of the transistors will only slightly increase the total area. Total area can also be reduced, by increasing the integrated resistance and reducing the size of the capacitors. This will also increase the amplifier gain. By using scaling capacitor techniques [12], the area can be further reduced.

Finally, it should be pointed that if all the transistors in two low noise circuits of similar topology, are assumed to operate in the same inversion level (ideally in weak inversion), and the circuits have the same supply voltage, the input referred noise voltage is related to power consumption in both circuits:

$$\frac{V_{n1}}{V_{n2}} = \sqrt{\frac{P_2}{P_1}} \tag{3}$$

Table 1: A comparative survey of 3 ENG amplifiers presented in ISCAS-2004.

|                    | Filter Band | Supply | Area               | Noise                    | Power |                   |

|--------------------|-------------|--------|--------------------|--------------------------|-------|-------------------|

| [7] Oses et al     | 100-5kHz    | 5V     | 1.1mm <sup>2</sup> | 5.1nV/Hz <sup>-1/2</sup> | 1mW   | Continuos<br>Time |

| [2] Uranga et al   | LP 3kHz     | 5V     | 2.7mm <sup>2</sup> | 6.6nV/Hz <sup>-1/2</sup> | 1.3mW | Chopper           |

| [1] Gosselin et al | 100-5kHz    | 1.8V   | reduced            | 30nV/Hz <sup>-1/2</sup>  | 25uW  | Chopper           |

Where  $V_n$  (  $\mathrm{nV}/\sqrt{\mathrm{Hz}}$  ) is the noise voltage and P is the power consumption. That shows that to reduce the noise voltage by 5, power consumption has to increase by 25, and so on. Equation (1) explains for example why the circuit in the last row of table 1 consumes such little power. The chopper amplifier presented in this work, has in the sense of (3), a noise-power consumption efficiency similar to the circuits in Table 1.

## 4. CONCLUSIONS

The designed amplifier shows that a chopper amplifier with simple topology can be used in ENG signals. Table 2 presents a summary of measurements results, and shows that the selected approach can lead to amplifiers with comparable noise and power consumption to those in Table 1, but with less area. It should also be noted that amplifiers described in [7] and [2] were developed in a 0.7 µm technology and [1] in a 0.18 µm.

Table 2: Measurements results.

|                 | Simulated                | Measured                  |  |

|-----------------|--------------------------|---------------------------|--|

| Gain            | 70                       | 80                        |  |

| Bandwidth       | 5000 Hz                  | 5000 Hz                   |  |

| CMRR            |                          | 88 dB                     |  |

| V. noise        | 4,0 nV/Hz <sup>1/2</sup> | 1,13 nV/Hz <sup>1/2</sup> |  |

| Consumption     |                          | 28 mW                     |  |

| Supply          | 5 V                      | 5 V                       |  |

| Area            | 1,0 mm <sup>2</sup>      |                           |  |

| Transistor area | 0,04 mm <sup>2</sup>     |                           |  |

# 5. ACKNOWLEDGEMENT.

The authors are grateful to the MOSIS MEP program for fabricating the circuit.

## 6. REFERENCES

- [1] B.Gosselin, V.Simard, "Low-power implantable microsystem intended to multichannel cortical recording", *IEEE ISCAS*'2004, vol.IV, pp.5-8, May-2004.

- [2] A.Uranga, N.Lago, X.Navarro, N.Barniol, "A low noise CMOS amplifier for ENG signals", *IEEE ISCAS'2004*, vol.IV, pp.21-24, May-2004.

- [3] W. Oswald and J. Mulder, "Dual Tone and Modem Frequency Generator with On-Chip Filters and Voltage Reference", *IEEE J. Solid-State Circuits*, vol SC-19, pp. 379-388, June 1984.

- [4] Enz, C.C., Temes, G.C., "Circuit techniques for reducing the effects of op-amp imperfections: autozeroing, correlated double sampling, and chopper stabilization", *Proceedings of the IEEE*, vol. 84, n°11, pp.1584 1614, Nov.1996.

- [5] Menolfi, C., Qiuting Huang, "A fully integrated, untrimmed CMOS instrumentation amplifier with submicrovolt offset", *IEEE J. Solid-State Circuits*, vol.34, n°3, pp.415-420, March 1999.

- [6] Bakker, A., Thiele, K., Huijsing, J.H., "A CMOS nested-chopper instrumentation amplifier with 100-nV offset", IEEE JSSC, vol.35, n°12, pp.1877 – 1883, Dec. 2000.

- [7] J.Sacristan, M.T.Oses, "Low noise amplifier for recording ENG signals in implantable systems", *IEEE ISCAS'2004*, vol.IV, pp.33-36, May-2004.

- [8] A.Arnaud, C.Galup Montoro, "Consistent noise models for analysis and design of CMOS circuits", *IEEE Trans. Circuits & Systems I*, Vol.51, n°10, pp.1909-1915, Oct.2004.

- [9] A.Bakker, J.H.Huijsing, "A CMOS Chopper Opamp with Integrated Low-Pass Filter", Proceedings ESSCIRC'97 – Southampton-UK, Sept.1997.

- [10] L.Tóth, Y.P.Tsividis, "Generalization of the Principle of Chopper Stabilization", IEEE TCAS—I, Vol.50, n°8, pp. 975-983, aug.2003.

- [11] A.Arnaud, "An efficient chopper amplifier, using a switched Gm-C filter technique", SBCCI 05, Florianopolis, Brazil, Sept.2005.

- [12] J.Silva Martínez, A.Vázquez González, "Impedance Scalers for IC Active Filters", Proc. IEEE ISCAS'98 Vol.1, pages 151-154