## SENSOR INTEGRADO DE TEMPERATURA ACONDICIONAMIENTO DE LA SEÑAL ANALÓGICA

Eduardo D. Baez, Walter Aróztegui, Andrés H. D'Alessandro, Antonio A. Quijano

Centro de Investigación y Desarrollo en Microelectrónica (CIDEM) Instituto Tecnológico de Buenos Aires (ITBA) Buenos Aires - Argentina

waroz@graffiti.net

### quijano@itba.edu.ar

#### RESUMEN

Se presenta parte del diseño de un circuito integrado destinado a la medición de temperatura, para el área aeroespacial, pero adaptable a otras aplicaciones. Se requieren sensores capaces de actuar en un amplio rango, con alta precisión y buena linealidad y por ello, se parte de detectores basados en resistores de platino que cumplen estas condiciones. Se analiza una posible estructura de amplificadores CMOS para el acondicionamiento de la señal analógica adquirida, teniendo en cuenta las limitaciones y efectos adversos que dicha tecnología puede introducir, especialmente el nivel de "offset", cuya disminución obliga a realizar un dis eño con "chopper".

### 1. INTRODUCCION

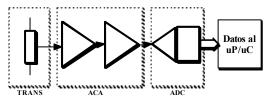

El proyecto propuesto (Fig.1) se compone de tres bloques: TRANS, ACA y ADC. El primero contiene el elemento transductor y circuitería asociada; ACA es el conjunto Acondicionador de señal y Amplificadores y el bloque ADC, es el Conversor Analógico-Digital.

Fig. 1-Bloques del Sensor Integrado de Temperatura

### 2. DESCRIPCION DE LOS BLOQUES

### 2.1.Bloque transductor (TRANS)

El transductor es del tipo resistivo, donde la conversión de energía se realiza por medio de la variación de la resistencia nominal a 0° C en función de la energía calórica que recibe. En particular se trata de un resistor de Platino (Pt) con resistencia típica a 0°C de 1000 ohms, de buena linealidad en un amplio rango de temperaturas y una respuesta suficientemente rápida.

La variación de la resistencia con la temperatura se puede expresar, con una buena aproximación, según la ecuación de Callendar-Van Dusen:  $R = R_0(1 + AT + BT^2)$ , donde para una Pt1000, los parámetros utilizados son: A = 3.9083e-3, B = -5.775e-7

# 2.2.Bloque ACA: Conjunto acondicionador de señal y amplificador

Este bloque trata de adaptar los niveles de impedancia entre el transductor y el circuito que le sigue, para que se produzca la mejor transferencia de energía de una etapa a la siguiente. Luego, la etapa amplificadora, ha de llevar a un nivel adecuado la señal producida por el transductor, para ser aplicada al conversor A/D y generar la información necesaria para el procesamiento de los datos.

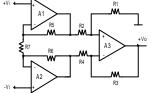

La señal eléctrica que genera el transductor es muy débil, (del orden de algunos milivolts), por lo que el conjunto acondicionador—amplificador debe cumplir restricciones especiales respecto de la relación señal a ruido, impedancia de entrada, ganancia y "offset". Se ha adaptado el clásico amplificador de instrumentación. (Fig. 2),

Fig.2-Amplificador de instrumentación

con las etapas A1 y A2 conformando un buffer diferencial de alta impedancia separando el transductor y el amplificador formado a partir de A3.

### 3. PROBLEMAS DE LOS AMPLIFICADORES

Como las señales que vamos a procesar están en el rango de las tensiones de "offset" (del orden de 10 mV en las celdas de amplificadores operacionales disponibles CMOS); y del ruido proporcional a 1/f de los amplificadores, se debe aplicar alguna técnica de reducción de tales efectos.[7]

La técnica de cancelación del offset que se eligió es la de "chopping" a fin de utilizar celdas estándar sin tener que desarrollar amplificadores totalmente a medida Por otro lado se facilita la generación de la señal de modulación, porque el modulador es una llave inversora de polaridad,

fácilmente realizable en CMOS, removiendo completamente el ruido 1/f

# 3.1. Cancelación de offset por medio de técnicas de "chopping":

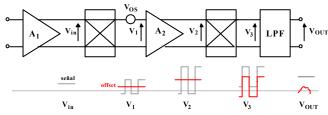

El "chopping" utiliza la modulación de la señal para trasladarla a una banda de frecuencias donde el ruido 1/f no está presente.

Fig. 4 – Cancelación de offset por choppeo.

Basaremos el diseño de nuestro bloque ACA de acuerdo al esquema de la Fig. 4, donde A<sub>1</sub> representa la etapa de entrada del amplificador de instrumentación, (A<sub>1</sub> y A<sub>2</sub> del gráfico del bloque ACA) y A<sub>2</sub> equivale a A<sub>3</sub> del bloque ACA).[3][5][6][8]

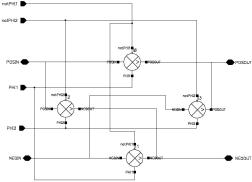

El "chopper" necesita dos señales de reloj de tipo "nonoverlapping" que se generan como se muestra en las Fig.5. [8]

Fig. 5- Generación de Clocks

El tercer amplificador del esquema general es el que introduce el offset que debe ser cancelado mediante la técnica de chopping.

Fig. 6-Amplificador A3

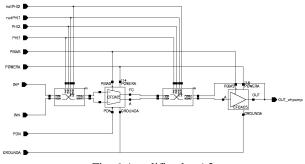

La Fig. 6 muestra el amplificador A3 con dos bloques (X) que realizan el "chopping"; una etapa de entrada "CFOAI5", y una etapa de salida: "CFOAO5" que son parte del amplificador CFOA55 AMI Semiconductors en la tecnología CMOS 0.7um.

Se ha conseguido reducir considerablemente el offset que introduce en el amplificador A3, que era del orden de 10mV y ahora a la salida no excede los 30uV.

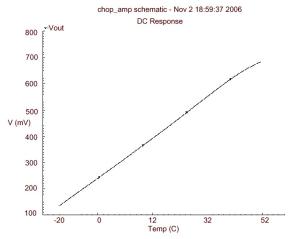

En la Fig.7 se puede observar la respuesta del bloque acondicionador de señal frente a una variación de temperatura entre -20 C y 52 C.[1][2]

Fig. 7- Respuesta del bloque ACA

#### 4. CONCLUSIONES Y TRABAJO FUTURO

Dado el comportamiento satisfactorio de las dos primeras etapas del proyecto que se ha descripto en este trabajo, se encuentra en desarrollo el pasaje a "layout" de los circuitos antes presentados[4]. En principio se utilizan celdas Standard de AMIS en tecnología de 0.7um por razones de accesibilidad y costo; sin embargo, para la aplicación aeroespacial que ha originado este proyecto, es posible que haya que utilizar tecnologías de dimensiones menores, mayor costo y mejor protección frente a los efectos de las radiaciones.

Se espera completar a la brevedad el diseño de la etapa de conversión A/D, y concluir con el resto del layout para poder llegar a la fabricación del prototipo.

### 5. REFERENCIAS

- [1] Baker, Circuit Design, Layout, and Simulation, IEEE Press Wiley InterScience, 2005.

- [2] Cadence Design Systems Manuals, 1999-2003

- [3] Coln, M. C. W. *Offset Cancelling Circuit*, IEEE Journal of Solid State Circuits, June 1989.

- [4] Hasting, A, *The Art of Analog Layout*, Practice Hall Upper Saddle River, NJ 07458, 2001

- [5] Kofi Makinwa *Dynamic Offset Cancellation Techniques*, IEEE Tutorials, <a href="http://www.ewh.ieee.org/tc/sensors/tutorials.htm/">http://www.ewh.ieee.org/tc/sensors/tutorials.htm/</a>, Delft University of Technology, 2002.

- [6] Messerschmitt, D. A Low Noise Chopper-Stabilized Differential Switched-Capacitor Filtering Technique, IEEE Journal of Solid State Circuits, 1981.

- [7] Razavi, Design of Analog CMOS Integrated Circuit, McGraw Hill. 2001.

- [8] Temes, G. C. and Enz, C. C. Circuit Techniques for Reducing the Efferts of OP-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper Stabilization, Proceedings of the IEEE, Nobember 1996.